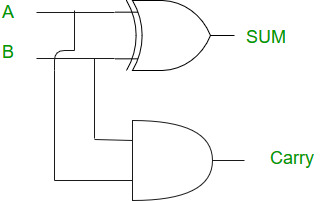

HALF ADDER:

module demux1x4(A, s0, s1, out0, out1, out2, out3);

Structural Model:

module hlfaddr(i1, i2, s, c);

input i1;

input i2;

output s;

output c;

xor(s,i1,i2);

and(c,i1,i2);

endmodule

input i1;

input i2;

output s;

output c;

xor(s,i1,i2);

and(c,i1,i2);

endmodule

module hlfaddr(i1, i2, s, c);

input i1;

input i2;

output s;

output c;

assign s=i1^i2;

assign c=i1&i2;

endmodule

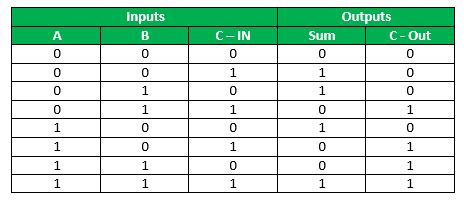

FULL ADDER:

Structural Model:

module fulladdr(a, b, cin, s, cout);

input a;

input b;

input cin;

output s;

wire s1,c1,c2;

xor n1(s1,a,b);

and n2(c1,a,b);

xor n3(s,s1,cin);

and n4(c2,s1,cin);

or n5(cout,c1,c2);

endmodule

Data Flow Model:

module fulladdr(a, b, cin, s, cout);

input a;

input cin;

output reg s;

output reg cout;

always@(a or b or cin)

begin

s=a^b^cin;

cout=a&b|(a^b)&cin;

end

endmodule

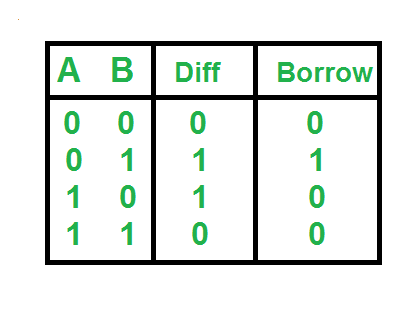

HALF SUBTRACTOR:

Structural Model:

module halfsub(i1, i2, d, b);

input i1;

input i2;

output d;

output b;

xor(d,i1,i2);

and(b,~i1,i2);

endmodule

Data Flow Model:

module halfsub(i1, i2, d, b);

input i1;

input i2;

output d;

output b;

assign d=i1^i2;

assign b=~i1&i2;

endmodule

FULL SUBTRACTOR:

Data Flow Model:

module fullsub(i1, i2, i3, d, b);

input i1;

input i2;

input i3;

output d;

output b;

assign d=i1^i2^i3;

assign b=(~i1&i2)|(~i1&i3)|(i3&i2);

endmodule

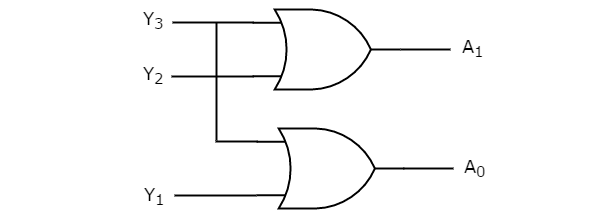

module enc4x2(i0, i1, i2, i3, out0, out1);

input i0;

input i1;

input i2;

input i3;

output out0;

output out1;

reg out0,out1;

always@(i0,i1,i2,i3)

case({i0,i1,i2,i3})

4'b1000:{out0,out1}=2'b00;

4'b0100:{out0,out1}=2'b01;

4'b0001:{out0,out1}=2'b11;

default: $display("invalid");

endcase

endmodule

DECODER:

input i0;

input i1;

output out0;

output out1;

output out2;

output out3;

reg out0,out1,out2,out3;

always@(i0,i1)

case({i0,i1})

2'b00:{out0,out1,out2,out3}=4'b1000;

2'b01:{out0,out1,out2,out3}=4'b0100;

2'b10:{out0,out1,out2,out3}=4'b0010;

2'b11:{out0,out1,out2,out3}=4'b0001;

default: $display("invalid");

endcase

endmodule

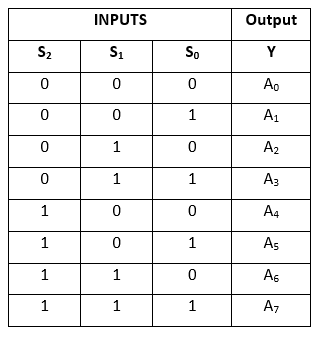

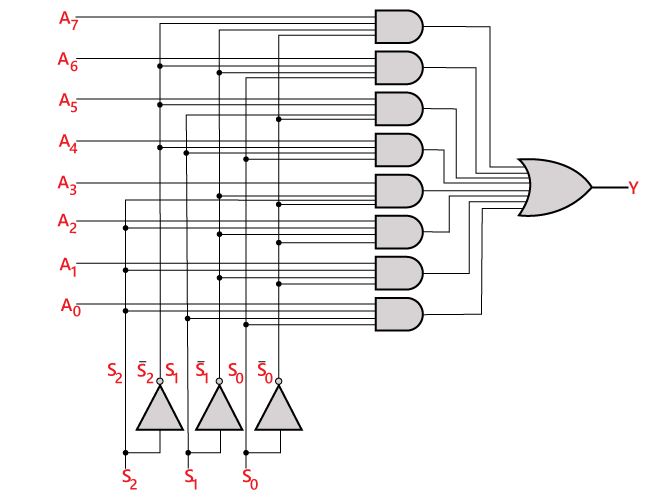

MULTIPLEXER (8:1)

module mux8x1(i1, i2, i3, i4, i5, i6, i7, i8, s1, s2, s3, out);

input i1;

input i2;

input i3;

input i4;

input i5;

input i6;

input i7;

input i8;

input s1;

input s2;

input s3;

output out;

always@(i1,i2,i3,i4,i5,i6,i7,i8,s1,s2,s3)

case({s1,s2,s3})

3'b000:out=i1;

3'b001:out=i2;

3'b010:out=i3;

3'b011:out=i4;

3'b100:out=i5;

3'b101:out=i6;

3'b110:out=i7;

3'b111:out=i8;

endcase

endmodule

MULTIPLEXER (4:1)

module mux4x1(i1, i2, i3, i4, s1, s2, out);

input i1;

input i2;

input i3;

input i4;

input s1;

input s2;

output out;

always@(i1,i2,i3,i4,s1,s2)

case({s1,s2})

2'b00:out=i1;

2'b01:out=i2;

2'b10:out=i3;

2'b11:out=i4;

endcase

endmodule

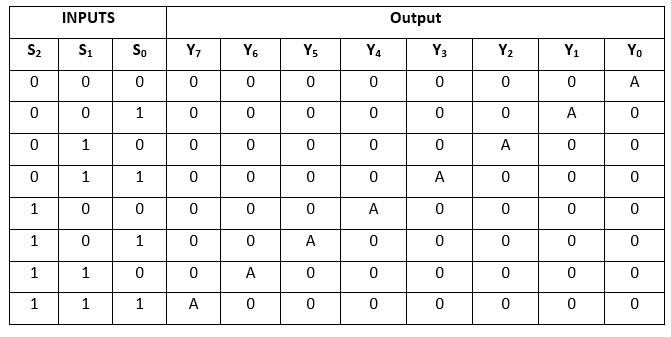

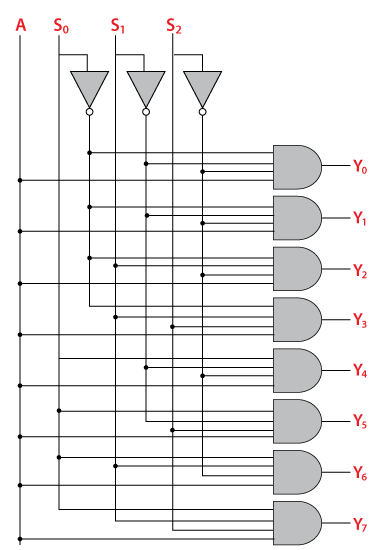

DEMULTIPLEXER (1:8)

module demux1x8(A, s0, s1, s2, out0, out1, out2, out3, out4, out5, out6, out7);

input s0;

input s1;

input s2;

output out0;

output out1;

output out2;

output out3;

output out4;

output out6;

output out7;

wire ns0,ns1,ns2;

not(ns0,s0);

not(ns1,s1);

not(ns2,s2);

and(out0,A,ns2,ns1,ns0);

and(out1,A,s2,ns1,ns0);

and(out2,A,ns2,s1,ns0);

and(out3,A,s2,s1,ns0);

and(out4,A,ns2,ns1,s0);

and(out5,A,s2,ns1,s0);

and(out6,A,ns2,s1,s0);

and(out7,A,s2,s1,s0);

endmodule

DEMULTIPLEXER (1:4)

input s0;

input s1;

output out0;

output out1;

output out2;

output out3;

wire ns0,ns1;

not(ns1,s1);

and(out0,A,ns1,ns0);

and(out1,A,s1,ns0);

and(out2,A,ns1,s0);

and(out3,A,s1,s0);

endmodule

RIPPLE CARRY ADDER

Data Flow Model:

module ripaddr(a, b, c, sum, cout);

input [7:0] a;

input [7:0] b;

input c;

output [7:0] sum;

output cout;

wire [8:0] temp;

assign temp=a+b+c;

assign sum=temp[7:0];

assign cout=temp[8];

endmodule

Structural Model:

module ripadder(a, b, sum, carry);

input [7:0] a;

input [7:0] b;

output [7:0] sum;

output [7:0] carry;

hlfaddr add1(a[0],b[0],sum[0],carry[0]);

fulladdr add2(a[1],b[1],carry[0],sum[1],carry[1]);

fulladdr add3(a[2],b[2],carry[1],sum[2],carry[2]);

fulladdr add4(a[3],b[3],carry[2],sum[3],carry[3]);

fulladdr add5(a[4],b[4],carry[3],sum[4],carry[4]);

fulladdr add6(a[5],b[5],carry[4],sum[5],carry[5]);

fulladdr add7(a[6],b[6],carry[5],sum[6],carry[6]);

fulladdr add8(a[7],b[7],carry[6],sum[7],carry[7]);

endmodule

MULTIPLIER

Data Flow Model:

module multiplier(a, b, out);

input [4:0] a;

input [4:0] b;

output [9:0] out;

assign out=a*b;

endmodule

Structural Model:

module multiply4bit(a, b, out);

input [3:0] a;

input [3:0] b;

output [7:0] out;

assign out[0]=a[0]&b[0];

wire x1,x2,x3,x4,x5,x6,x7,x8,x9,x10,x11,x12,x13,x14,x15,x16,x17;

hlfaddr ha1(out[1],x1,(a[1]&b[0]),(a[0]&b[1]));

fulladdr fa1(x2,x3,(a[1]&b[1]),(a[0]&b[2]),x1);

fulladdr fa2(x4,x5,(a[1]&b[2]),(a[0]&b[3]),x3);

hlfaddr ha2(x6,x7,(a[1]&b[3]),x5);

hlfaddr ha3(out[2],x15,x2,(a[2]&b[0]));

fulladdr fa5(x14,x16,x4,(a[2]&b[1]),x15);

fulladdr fa4(x13,x17,x6,(a[2]&b[2]),x16);

fulladdr fa3(x9,x8,x7,(a[2]&b[3]),x17);

hlfaddr ha4(out[3],x12,x14,(a[3]&b[0]));

fulladdr fa8(out[4],x11,x13,(a[3]&b[1]),x12);

fulladdr fa7(out[5],x10,x9,(a[3]&b[2]),x11);

fulladdr fa6(out[6],out[7],x8,(a[3]&b[3]),x10);

endmodule

module fulladdr(s, cout, a, b, cin); //STORE BY CREATING ANOTHER VERILOG MODULE

input a;

input b;

input cin;

output s;

output cout;

assign s=a^b^cin;

assign cout=((a&b)|(a&cin)|(b&cin));

endmodule

module hlfaddr(s, c, i1, i2); //STORE BY CREATING ANOTHER VERILOG MODULE

input i1;

input i2;

output s;

output c;

assign s=i1^i2;

assign c=i1&i2;

endmodule

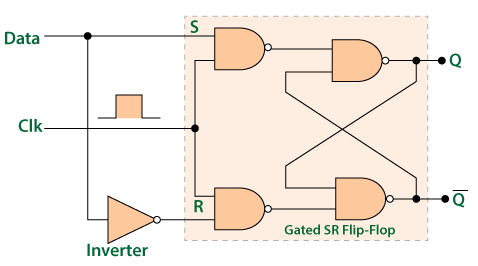

D FLIPFLOP

module dflipflop(d, clk, res, q1, q2);

input d;

input clk;

input res;

output q1;

output q2;

reg q1,q2;

always@(posedge clk)

begin

if(res)

q1=0;

q2=1;

end

else

begin

q1=d;

end

end

endmodule

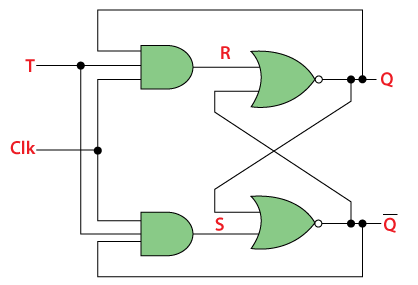

T FLIPFLOP

module tflipflop(clk, res, t, q);

input clk;

input res;

input t;

output q;

reg q;

if(~res)

q=0;

else

if(t)

q=(~q);

else

q=q;

endmodule

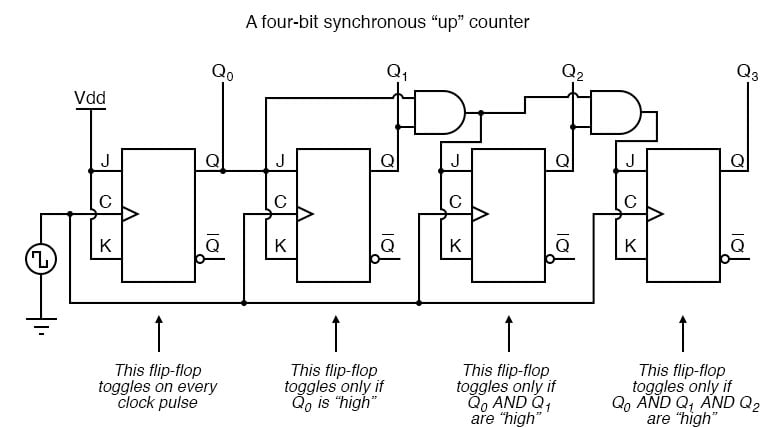

module counter(clock, clear, q);

input clock;

input clear;

output reg [3:0] q;

always@(posedge clear or posedge clock)

if(clear)

q<=0;

else

q<=q+1;

endmodule

PRBS GENERATOR

module prbs(d, clk, res, q);

input [3:0] d;

input clk;

input res;

output [3:0] q;

reg [3:0]q;

reg [3:0]temp;

if(res)

q=0;

else

begin

temp=d;

temp[3]=temp[0]^temp[3];

q=temp<<1;

end

end

endmodule

MEALY STATE MACHINE

module mealy(clk, rst, inp, outp);

input clk;

input rst;

input inp;

output outp;

reg [1:0] state;

reg outp;

always@(posedge clk,posedge rst)

begin

if(rst)

begin

state<=2'b00;

outp<=0;

end

else

begin

case(state)

2'b00:

begin

if(inp)

begin

state<=2'b01;

outp<=0;

end

else

begin

state<=2'b10;

outp<=0;

end

end

2'b01:

begin

if(inp)

begin

state<=2'b00;

outp<=1;

end

else

begin

state <= 2'b10;

outp <= 0;

end

end

2'b10:

begin

if(inp)

begin

state<=2'b01;

outp<=0;

end

else

begin

state<=2'b00;

outp<=1;

end

end

default:

begin

state <= 2'b00;

outp <= 0;

end

endcase

end

end

endmodule

MOORE STATE MACHINE

module moore(clk, rst, inp, outp);

input clk;

input rst;

input inp;

output outp;

reg [1:0] state;

reg outp;

always@(posedge clk,posedge rst)

begin

if(rst)

state<=2'b00;

else

begin

case(state)

2'b00:

begin

if(inp)

state<=2'b01;

else

state<=2'b10;

end

2'b01:

begin

if(inp)

state<=2'b11;

else

state<=2'b10;

end

2'b10:

begin

if(inp)

state<=2'b01;

else

state<=2'b11;

end

2'b11:

begin

if(inp)

state<=2'b01;

else

state<=2'b10;

end

endcase

end

end

always @(posedge clk, posedge rst)

begin

if(rs )

outp<=0;

else if(state==2'b11 )

outp<=1;

else

outp<=0;

end

endmodule

CARRY SELECT ADDER

module carryselectadder(a, b, cin, sum, cout);

input [7:0] a;

input [7:0] b;

input cin;

output [7:0] sum;

output cout;

wire c,c_top,c_bot;

wire [3:0]s_top,s_bot;

rcast

r1(a[3:0],b[3:0],cin,sum[3:0],c),

r2(a[7:4],b[7:4],0,s_bot[3:0],c_bot),

r3(a[7:4],b[7:4],1,s_top[3:0],c_top);

mux2

m1(s_top[0],s_bot[0],c,sum[4]),

m2(s_top[1],s_bot[1],c,sum[5]),

m3(s_top[2],s_bot[2],c,sum[6]),

m4(s_top[3],s_bot[3],c,sum[7]),

m5(c_top,c_bot,c,cout);

endmodule

module rcast(a, b, c, s, ca);

input [3:0] a;

input [3:0] b;

input c;

output [3:0] s;

output ca;

wire c1,c2,c3;

fulladdr

f1(a[0],b[0],c,s[0],c1),

f2(a[1],b[1],c1,s[1],c2),

f3(a[2],b[2],c2,s[2],c3),

f4(a[3],b[3],c3,s[3],ca);

endmodule

module fulladdr(a, b, cin, s, cout);

input a;

input b;

input cin;

output s;

output cout;

assign s=a^b^cin;

assign cout=(a&b)|(b&cin)|(cin&a);

endmodule

module mux2(i0, i1, s0, y);

input i0;

input i1;

input s0;

output y;

wire s0bar,p,q;

not n1(s0bar,s0);

and a1(p,i0,s0bar),a2(q,i1,s0);

or o1(y,p,q);

endmodule

MICROWIND

INVERTER(not GATE)

Comments

Post a Comment